OMNITRADE NEWS

La DDR6 Révolutionne la Mémoire Vive : Performances Inédites et Transition Imminente

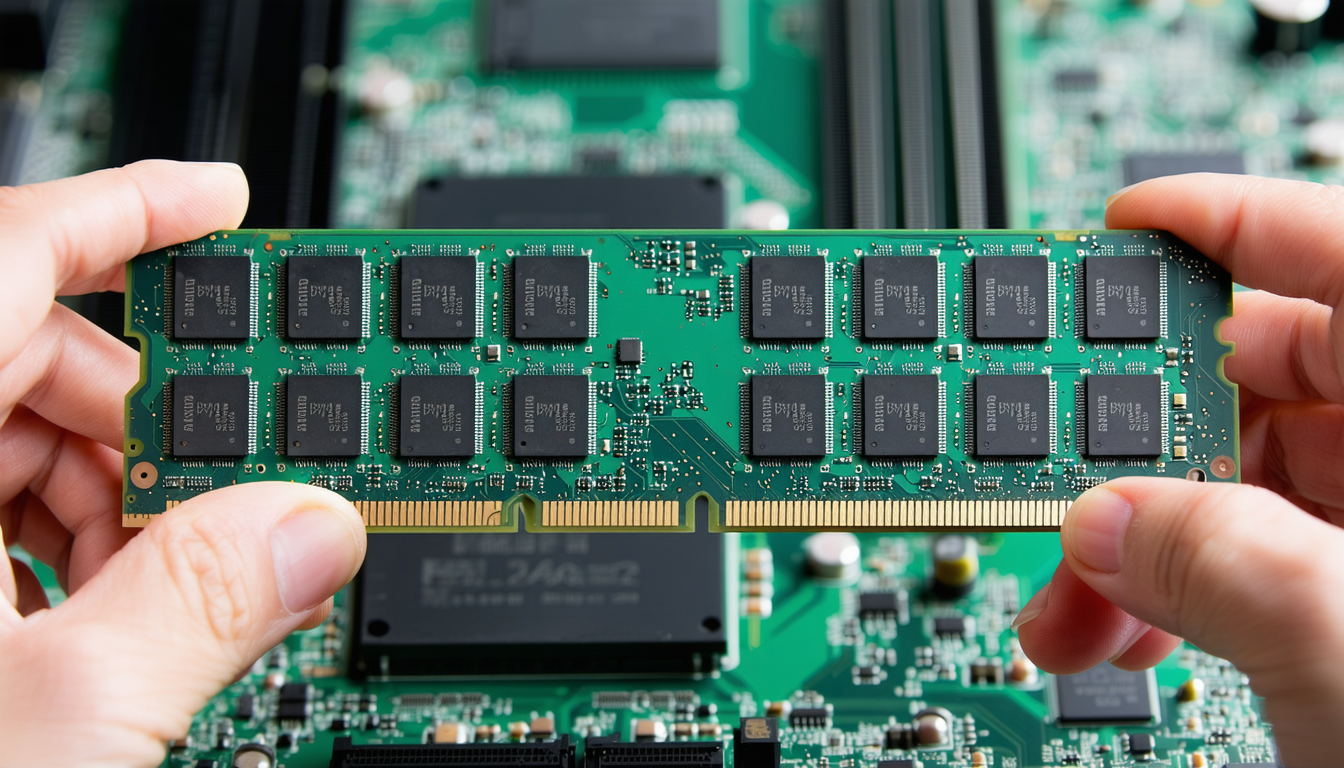

La mémoire vive est à l’aube d’une révolution majeure avec l’arrivée imminente de la DDR6. Promettant de tripler les performances de la DDR5 tout en réduisant drastiquement la consommation électrique, cette nouvelle génération, capable d’atteindre des débits de 8 800 à 17 600 MT/s, s’apprête à redéfinir les standards de l’informatique.

Le consortium JEDEC a déjà officialisé le standard LPDDR6 pour les appareils mobiles en juillet 2025, avec une production de masse lancée au quatrième trimestre. Pour les ordinateurs de bureau, la norme DDR6 sera finalisée début 2026, mais les premiers modules grand public ne devraient pas être disponibles avant 2027, à des tarifs initialement trois à quatre fois supérieurs à ceux de la DDR5.

Cette transition ne sera pas sans contraintes : la DDR6 exigera de nouvelles cartes mères et processeurs, abandonnant toute rétrocompatibilité. Intel et AMD préparent activement leurs plateformes respectives pour accueillir cette technologie de pointe, marquant un tournant décisif pour l’industrie.

Sélection de la rédaction

Analyse Approfondie : La DDR6 sous toutes ses coutures

Calendrier et Coûts : Anticiper la Transition

Le déploiement de la DDR6 s’échelonne sur plusieurs années. Le standard LPDDR6 pour les appareils mobiles a été officialisé par JEDEC en juillet 2025, avec une production de masse par SK Hynix dès le quatrième trimestre 2025. Pour la DDR6 standard destinée aux ordinateurs de bureau et serveurs, la finalisation du standard est attendue entre fin 2025 et début 2026. Les premiers échantillons seront disponibles pour les fabricants dès le troisième trimestre 2025, mais la production de masse n’est pas envisagée avant fin 2026. Les kits grand public n’arriveront en magasin qu’en 2027, avec un volume significatif prévu pour 2029-2030.

Concernant les tarifs, la DDR6 représentera un investissement conséquent à son lancement. Un module CAMM2 de 32 Go en DDR6-12800 devrait coûter environ 500 USD en 2027, soit trois à quatre fois le prix d’un kit DDR5 équivalent. Les kits premium DDR6-17600+ dépasseront les 300 USD en phase précommerciale (2026). Une baisse progressive est attendue : la parité avec la DDR5 haut de gamme pourrait être atteinte fin 2027, et d’ici 2029, la DDR6 devrait devenir le standard dominant avec des prix inférieurs à 150 USD pour 32 Go.

Plateformes et Compatibilité : Un Changement Radical

La transition vers la DDR6 implique un changement complet de plateforme. Il n’y aura aucune rétrocompatibilité avec la DDR4 ou la DDR5, rendant l’acquisition de nouvelles cartes mères et processeurs obligatoire. Intel devrait être le premier à intégrer le support DDR6 avec ses processeurs Panther Lake (architecture 18A) début 2026, accompagnés des chipsets Z990 et W990. Les cartes mères Intel seront équipées exclusivement de slots CAMM2.

Du côté d’AMD, la feuille de route est plus prudente. Les serveurs Epyc basés sur Zen 6 supporteront la DDR6 dès le second semestre 2026. Pour le grand public, la plateforme AM6, avec les processeurs Ryzen 8000/9000 (Zen 7), arrivera courant 2027 avec un support natif de la DDR6. Les cartes mères DDR6 introduiront également de nouvelles fonctionnalités, telles qu’une alimentation mémoire améliorée (PMIC intégré au CAMM2), un refroidissement actif sur les slots et le support du SPD Hub avec intégration I3C. Le format CAMM2, plus plat, réduit l’impédance et améliore la signalisation, mais nécessite des connecteurs spécifiques.

Innovations Architecturales : Le Secret des Performances

L’architecture de la DDR6 représente une rupture technologique majeure par rapport aux générations précédentes. Alors que la DDR5 utilisait une architecture à deux sous-canaux indépendants de 32 bits (2×32 bits), la DDR6 adopte une conception radicalement différente avec quatre sous-canaux de 24 bits chacun. Cela porte le total à 96 bits par rang, une augmentation significative qui est la clé de l’explosion de la bande passante et des débits annoncés.

Cette subdivision en quadruples sous-canaux permet une gestion des données beaucoup plus fine et efficace, réduisant la latence et augmentant considérablement le parallélisme des opérations. Combinée à des puces gravées en 1c nm (troisième génération 10 nm), cette architecture repensée est le moteur des performances triplées promises par la DDR6, tout en optimisant la consommation électrique pour répondre aux exigences des systèmes de nouvelle génération.